- 55 views

See https://www.icaslab.com/Seminar

Meeting Link:

https://teams.microsoft.com/l/meetup-join/19%3ameeting_YWQ4NzcyYjMtYmZjNC00MTNjLTk4NTItYjRkOTFmYjk3NTRk%40thread.v2/0?context=%7b%22Tid%22%3a%224b2a4b19-d135-420e-8bb2-b1cd238998cc%22%2c%22Oid%22%3a%225fc2170a-7068-4a33-9021-df11b94ba696%22%7d

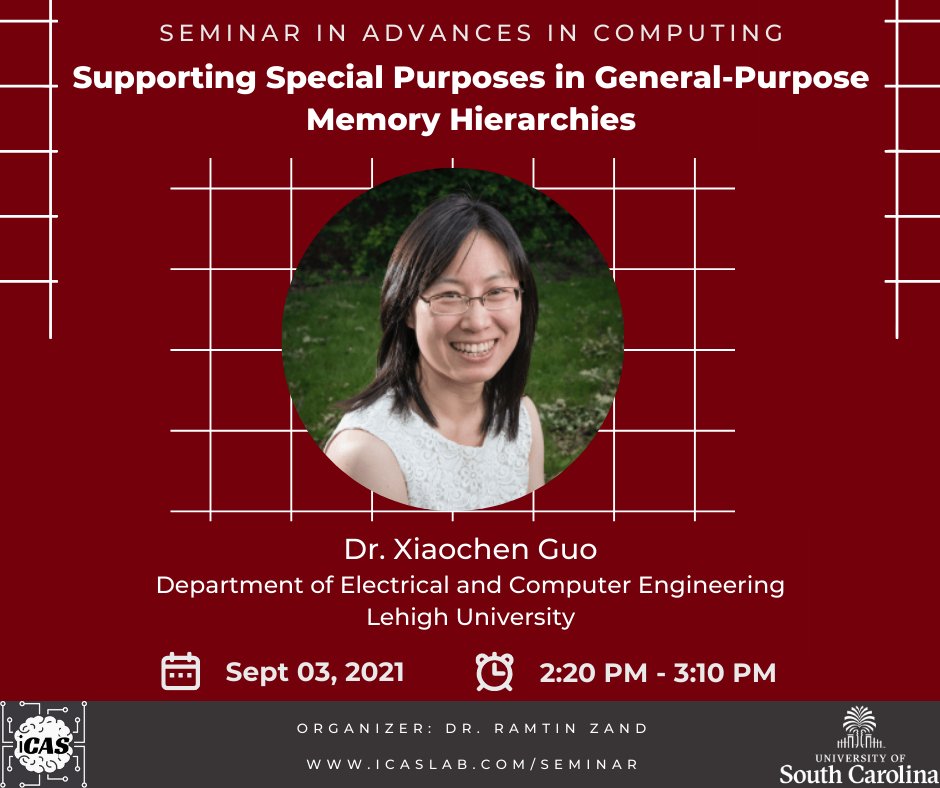

BIO: Dr. Xiaochen Guo is an associate professor in the Department of Electrical and Computer Engineering at Lehigh University. Dr. Guo received her Ph.D. degree in Electrical and Computer Engineering from the University of Rochester, and received the IBM Ph.D. Fellowship twice. Dr. Guo’s research interests are in the broad area of computer architecture, with an emphasis on leveraging emerging technologies to build energy-efficient microprocessors and memory systems. Dr. Guo is an IEEE senior member and a recipient of the National Science Foundation CAREER Award, the P. C. Rossin Assistant Professorship, and the Lawrence Berkeley National Laboratory Computing Sciences Research Pathways Fellowship.

ABSTRACT: General-purpose computing systems employ memory hierarchies to provide the appearance of a single large, fast, and coherent memory for general applications with good locality. However, conventional memory hierarchies cannot provide sufficient isolation for security workloads, support richer semantics, or hide memory latency for irregular memory accesses. This talk will present two of our recent works aiming to address these special needs in important workloads. In the first work, we propose to add a virtually addressed, set-associative scratchpad (SPX64) to a general-purpose CPU to support isolation and hash lookups in security and persistent applications. The proposed scratchpad is placed alongside of a traditional cache, and is able to avoid many of the programming challenges associated with traditional scratchpads without sacrificing generality. SPX64 delivers increased security and improves performance. In the second work, a software-assisted hardware prefetcher is proposed, which focuses on repeating irregular memory access patterns for data structures that cannot benefit from conventional memory hierarchies and hardware prefetchers. The key idea is to provide a programming interface to record cache miss sequence on the first appearance of a memory access pattern and prefetch through replaying the pattern on the following repetitions. By leveraging the programmer knowledge, the proposed Record-and-Replay (RnR) prefetcher can achieve over 95% prefetching accuracy and miss coverage.