Note Title 4/5/2009

## CSCE211, Homework Assignment No. 5

- · Show all your steps—answers alone are not sufficient.

- · Homework must be done neatly

- · Use straight-edged paper (no notebook tear-outs with ragged edges)

- · STAPLE papers to a signed cover sheet.

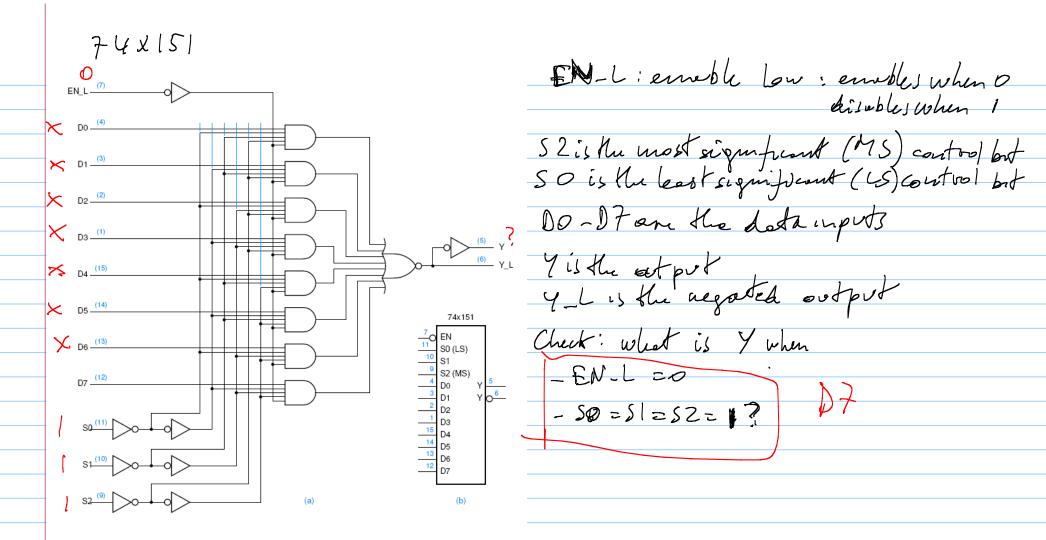

Please print the following for reference and for this assignment: MUX-Decoder instructions. Also, please print for reference and inclusion in your Homework paper MSI diagrams 74LS151 (8-to-1 MUX) and 74LS138 (3-to 8 Decoder/De-MUX)

- 1. Use a 74x151 (8-to-1 MUX) to implement f(W, X, Y, Z) = Sm(2, 4, 7, 8, 9, 13, 14). Use the "rowpairs" method shown in class. Show all enable and address connections. (20pts) (See instructions above.)

- 2. Use a 74x138 decoder and an external AND gate to implement f(X, Y, Z) = Sm(1, 2, 4, 5, 6). Show all enable and address connections. (HINT: AND the MAX terms) (20pts) (See instructions above)

- 3. Use a 74x138 decoder and an external NAND gate to implement f(p, q, r) = Sm(1, 3, 7). Show all enable and address connections. (20 pts) (See instructions above)

- 4. Design an 8-to-1 MUX from *three* 4-to-1 MUXs. Label the inputs on each 4-to1 MUX as I0 to I3. In the "first stage," place one MUX on "top" of another and connect their select lines S1 (most significant) and S0 together. Let I0 on the "top" MUX correspond to D0 of 8 inputs and let I0 on the "bottom" MUX be D4. Use the third MUX to select between the **two** "first-stage" MUX outputs. You can configure a 4-to-1 MUX to be a 2-to-1 MUX by setting its MS select line to logic "0." When you finish, label the three 8-to-1 select lines as S2 (most significant) to S0 (least significant). (20 pts)

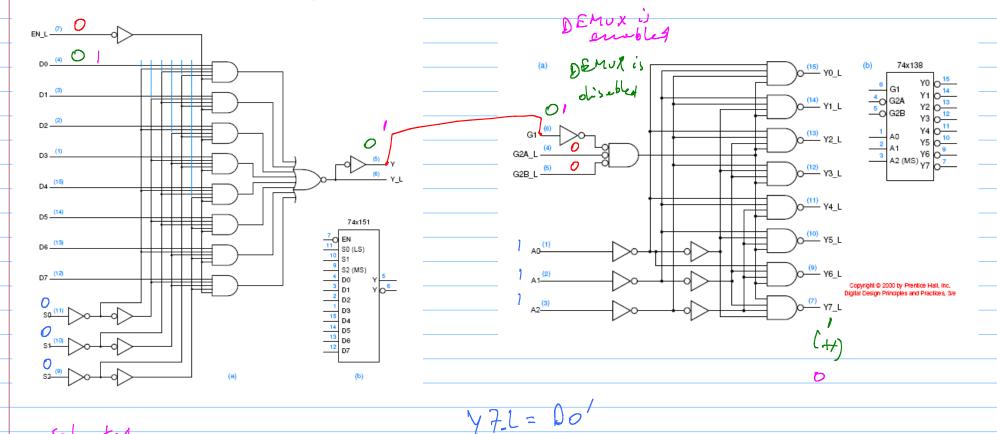

- 5. Design an 8-input to 8-output MUX-DEMUX system using a 74x151 for the MUX part and a 74x138 for the DEMUX. Leave the outputs of the 74x138 as *active-low* signals (leave the output bubbles as-is). Configure ("hard wire") the select-lines values on the MUX and address-lines values on the DEMUX so that *input* **D4** is routed to *output* **Y6\_L**. Wire so that there is only **one** active low ENABLE signal that controls **both** chips. You can do this because there are 3 enable lines (one active high, two active low) on the DECODER (20pts).

file:///Cl/Courses/csce211sp09/hw5Files/homework5.htm4/5/2009 11:48:12 AM

See the Motoro la doto sheet, which is linked to the course web site. Note that it provides a truth table on uses different nonnes for the variable, 5. Design an 8-input to 8-output MUX-DEMUX system using a 74x151 for the MUX part and a 74x138 for the DEMUX. Leave the outputs of the 74x138 as *active-low* signals (leave the output bubbles as-is). Configure ("hard wire") the select-lines values on the MUX and address-lines values on the DEMUX so that *input* **D4** is routed to *output* **Y6\_L**. Wire so that there is only **one** active low ENABLE signal that controls **both** chips. You can do this because there are 3 enable lines (one active high, two active low) on the DECODER (20pts).

file:///C|/Courses/csce211sp09/hw5Files/homework5.htm4/5/2009 11:48:12 AM

The 74x138 Decoder can be used as a derwltipler (DEMUX), as explained on the Motorole date sheet (linked to course web site):

one the high Enable line for in.

Note Title 4/5/2009

## CSCE211, Homework Assignment No. 5

- · Show all your steps—answers alone are not sufficient.

- · Homework must be done neatly

- · Use straight-edged paper (no notebook tear-outs with ragged edges)

- · STAPLE papers to a signed cover sheet.

Please print the following for reference and for this assignment: MUX-Decoder instructions. Also, please print for reference and inclusion in your Homework paper MSI diagrams 74LS151 (8-to-1 MUX) and 74LS138 (3-to 8 Decoder/De-MUX)

- 1. Use a 74x151 (8-to-1 MUX) to implement f(W, X, Y, Z) = Sm(2, 4, 7, 8, 9, 13, 14). Use the "rowpairs" method shown in class. Show all enable and address connections. (20pts) (See instructions above.)

- 2. Use a 74x138 decoder and an external AND gate to implement f(X, Y, Z) = Sm(1, 2, 4, 5, 6). Show all enable and address connections. (HINT: AND the MAX terms) (20pts) (See instructions above)

- 3. Use a 74x138 decoder and an external NAND gate to implement f(p, q, r) = Sm(1, 3, 7). Show all enable and address connections. (20 pts) (See instructions above)

- 4. Design an 8-to-1 MUX from *three* 4-to-1 MUXs. Label the inputs on each 4-to1 MUX as I0 to I3. In the "first stage," place one MUX on "top" of another and connect their select lines S1 (most significant) and S0 together. Let I0 on the "top" MUX correspond to D0 of 8 inputs and let I0 on the "bottom" MUX be D4. Use the third MUX to select between the **two** "first-stage" MUX outputs. You can configure a 4-to-1 MUX to be a 2-to-1 MUX by setting its MS select line to logic "0." When you finish, label the three 8-to-1 select lines as S2 (most significant) to S0 (least significant). (20 pts)

- 5. Design an 8-input to 8-output MUX-DEMUX system using a 74x151 for the MUX part and a 74x138 for the DEMUX. Leave the outputs of the 74x138 as *active-low* signals (leave the output bubbles as-is). Configure ("hard wire") the select-lines values on the MUX and address-lines values on the DEMUX so that *input* **D4** is routed to *output* **Y6\_L**. Wire so that there is only **one** active low ENABLE signal that controls **both** chips. You can do this because there are 3 enable lines (one active high, two active low) on the DECODER (20pts).

file:///Cl/Courses/csce211sp09/hw5Files/homework5.htm4/5/2009 11:48:12 AM

Exercise 9.1(b) entext

(except for use of 4-1 Mux

configured tobe @2-1Mi

chick the

books

For exercise 5 (Qviz 9)

selected

and routed to output

for ho mework? scleet input Dy end voute: + to output Yb-L See instructions linked to HW5 page for exercises 3, 4, and 5.